## EEL 4783: HDL in Digital System Design

#### Lecture 7: HDL Programming for Logic Synthesis

Prof. Mingjie Lin

**Stands For Opportunity**

## How to Write Synthesis-Friendly HDL Codes?

- Detect and eliminate redundant logic?

- Detect combinational feedback feedback loops

- Exploit Don't care conditions

- Detect unused states

- Detect and collapse equivalent states

- Synthesize optimized logic circuits

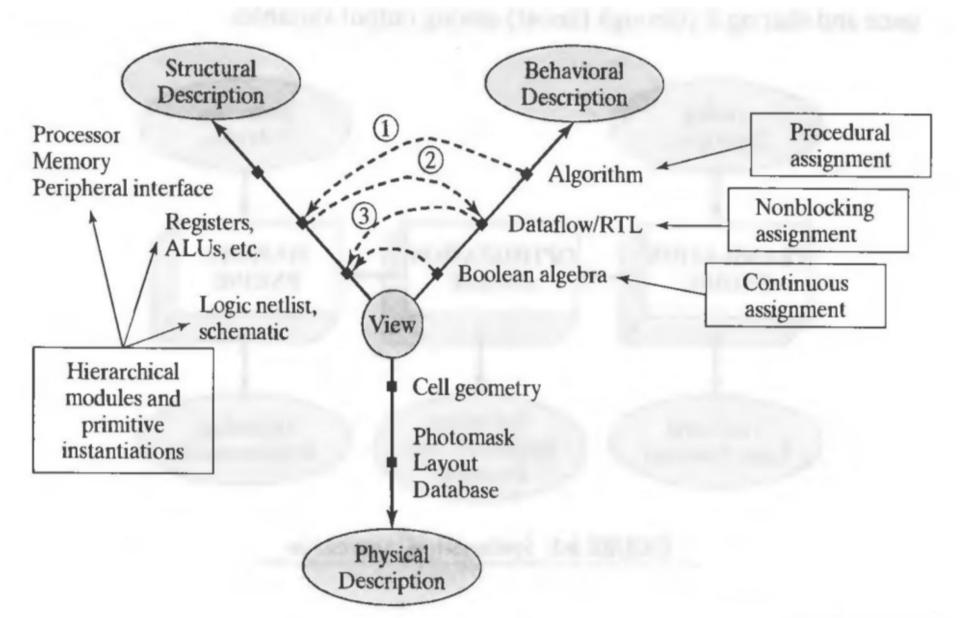

#### Behavioral, Structural, Physical Views

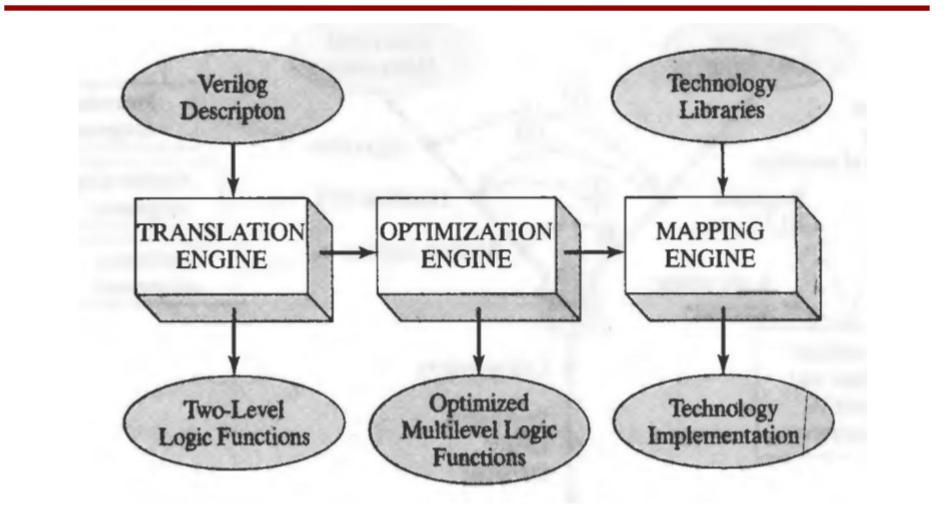

#### Synthesis Tools Organization

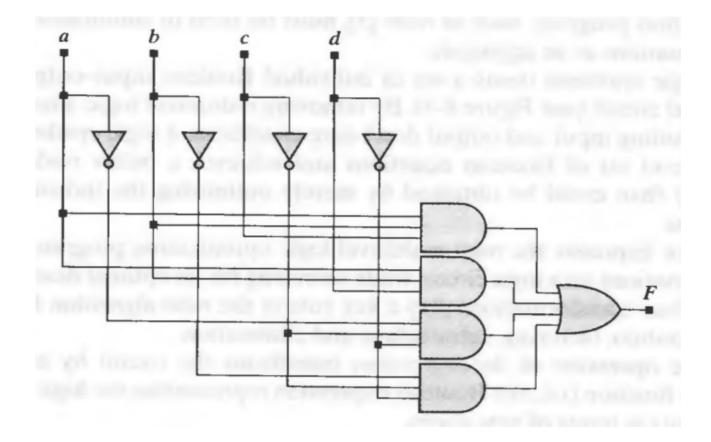

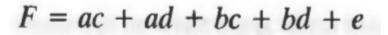

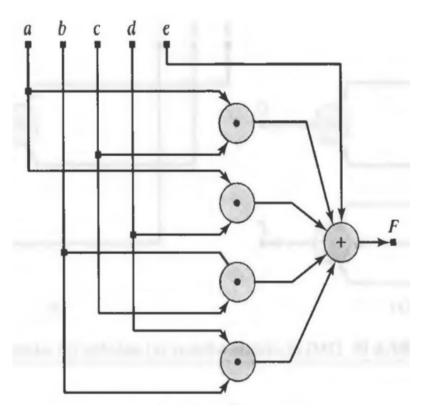

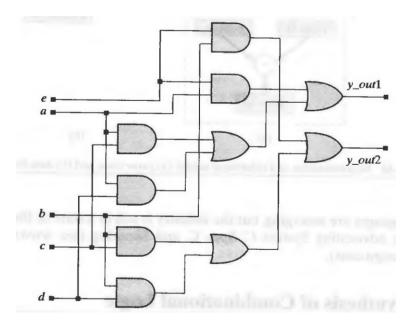

#### **Sum-of-Products Implementations**

F = abc + abd + a'b'c' + b'c'd'

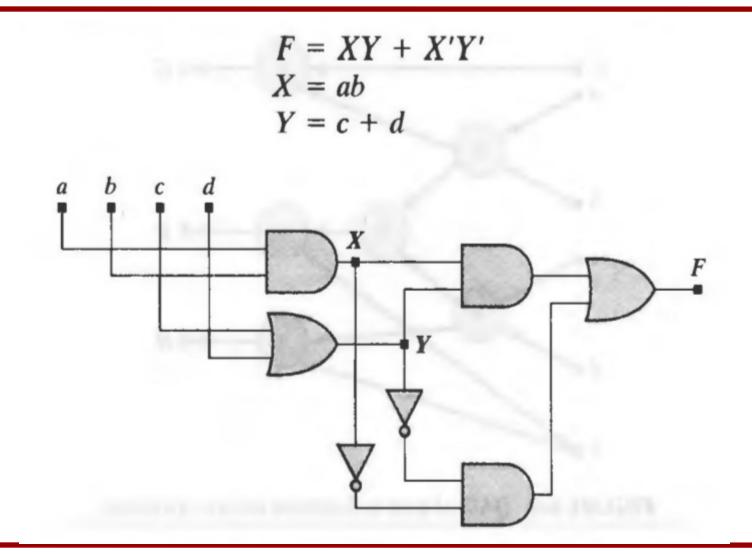

### **Optimized Design**

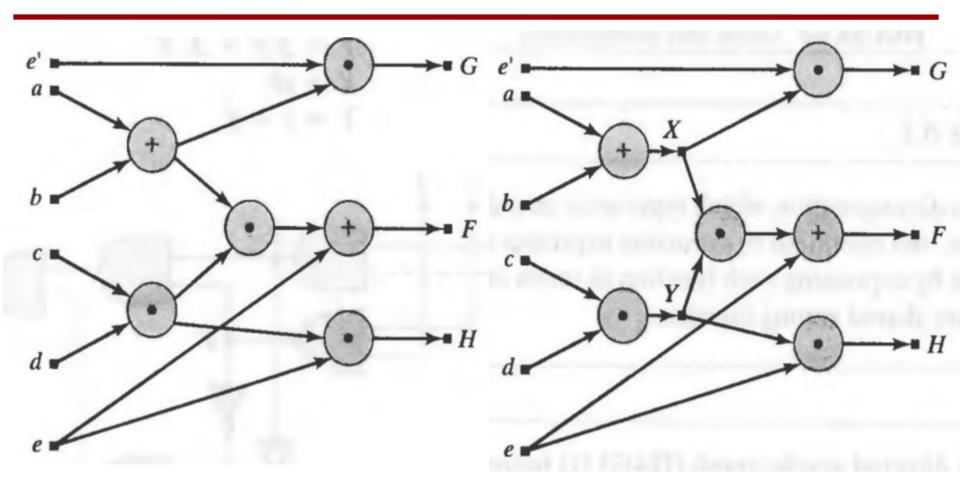

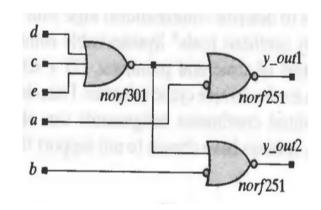

## DAG Graph

$$F = (a + b)(c + d) + e$$

# Logic Optimization

### Synthesis of Comb. Circuits

| output    | _opt(y_out1, y_out2, a, b, c, d, e);<br>y_out1, y_out2; |

|-----------|---------------------------------------------------------|

| input     | a, b, c, d, e;                                          |

| and       | (y1, a, c);                                             |

| and       | (y2, a, d);                                             |

| and       | (y3, a, e);                                             |

| or        | (y4, y1, y2);                                           |

| or        | (y_out1, y3, y4);                                       |

| and       | (y5, b, c);                                             |

| and       | (y6, b, d);                                             |

| and       | (y7, b, e);                                             |

| or        | (y8, y5, y6);                                           |

| or        | (y_out2, y7, y8);                                       |

| endmodule | I promitive data frances in a set                       |

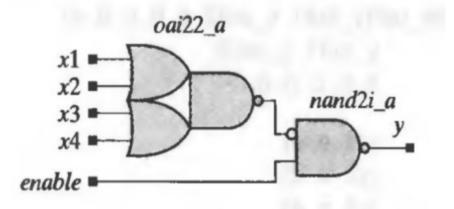

module or\_nand (y, enable, x1, x2, x3, x4);

output y;

input enable, x1, x2, x3, x4;

assign y = ~(enable & (x1 | x2) & (x3 | x4));

endmodule

```

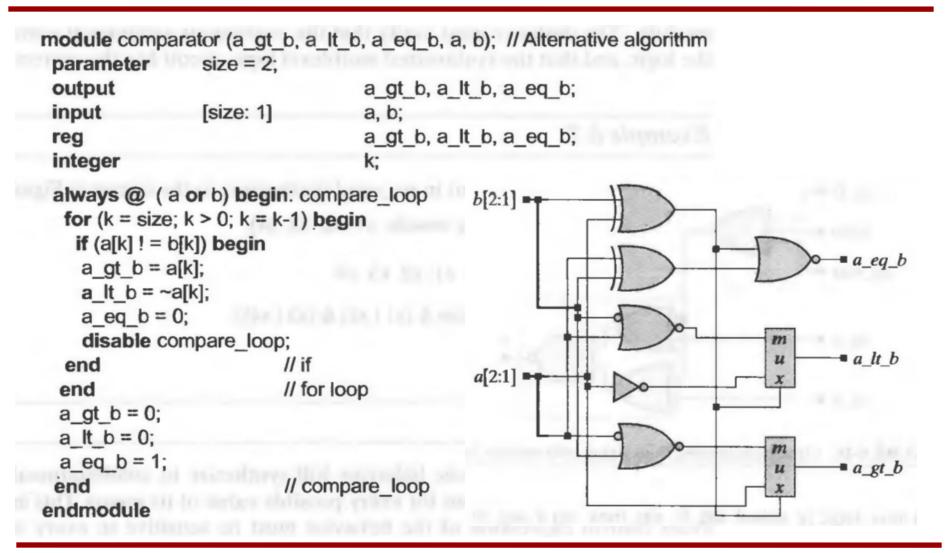

module comparator (a_gt_b, a_lt_b, a_eq_b, a, b); // Alternative algorithm

parameter

size = 2;

output

a gt b, a lt b, a eq b;

input

[size: 1]

a, b;

a_gt_b, a_lt_b, a_eq_b;

reg

integer

k;

always @ ( a or b) begin: compare loop

for (k = size; k > 0; k = k-1) begin

if (a[k] ! = b[k]) begin

a_gt_b = a[k];

a It b = -a[k];

a_eq_b = 0;

disable compare loop;

end

// if

end

// for loop

a_gt_b = 0;

a It b = 0;

a eq b = 1;

end

// compare loop

endmodule

```

#### **Final issues**

- Please fill out the student info sheet before leaving

- Come by my office hours (right after class)

- Any questions or concerns?