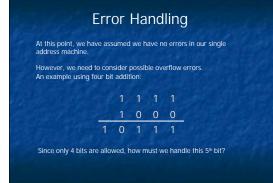

#### Overflow

The addition of a flip/flop to our ALU would enable us to check for this overflow situation.

The CPU has to check for an interrupt each time an instruction is executed.

Therefore, we need to add a new command to the ISA, the Interrupt Cycle (05 ABEND).

At the end of each execution cycle, the DECODER will be set to 05 instead of 00, to check for interrupts at the end of each execution cycle.

Halting at this step enables us to prevent inconsistent data.

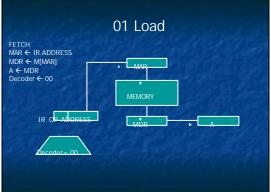

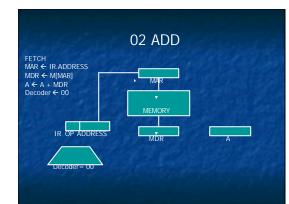

#### ISA Interrupt Cycle 02 ADD 01 LOAD MAR ← IR.ADDRESS MAR ← IR.ADDRESS MDR ← M[MAR] MDR ← M[MAR] A ← MDR A ← A + MDR 03 STORE 04 END 05 Int. Handler Routine IF OV = 1 then HALT MAR ← IR.ADDRESS DECODER ← 00 MDR ← A M[MAR] ← MDR

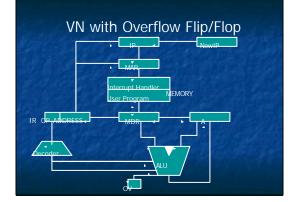

#### Interrupt Handler

Instead of stopping the program when an overflow is encountered, the flow of execution is simply passed to an Interrupt Handler.

This also allows us to take advantage of pipelining since the program is not halted.

To do this, the program counter (IP) is loaded with the start address of the interrupt handler in memory from NEWIP.

05 ABEND IF OV = 1 then IP  $\leftarrow$  NEWIP DECODER  $\leftarrow$  00

## Virtual Machine The Interrupt Handler is the first extension layer of the "Virtual Machine". This is the first step towards an operating system.

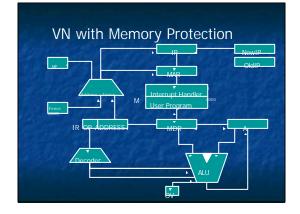

#### Shared Memory

Like any other program, the Interrupt Handler must be loaded into memory.

However, this may lead to a new problem if the currently loaded program tries to modify the interrupt handler's routine.

We need some way to protect the interrupt handler's routine from being modified by the currently loaded program.

#### **Memory Protection**

We protect the interrupt handler's routine by adding three components:

Fence Register - Register loaded with the address of the boundary between the interrupt handler routine and the user program.

Device for Address Comparison – compares the fence register with any addresses that the user program attempts to access.

Flip/Flop – The flip/flop is set to 1 if a memory violation occurs

# Updated ISA

IF MP = 0 then MDR  $\leftarrow$  M[MAR] A  $\leftarrow$  MDR DECODER  $\leftarrow$  05

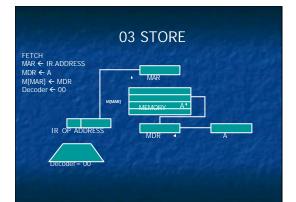

#### 03 STORE

$MAR \leftarrow IR.ADDRESS$ IF MP = 0 then MDR \leftarrow A M[MAR] \leftarrow MDR

#### **O2 ADD** MAR $\leftarrow$ IR.ADDRESS IF MP = 0 then MDR $\leftarrow$ M[MAR] A $\leftarrow$ A + MDR

05 Int. Handler Routine IF OV = 1 IP ← NEWIP IF MP = 1 IP ← NEWIP DECODER ← 00

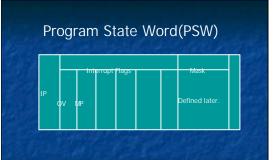

#### Program State Word(PSW)

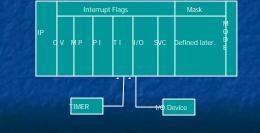

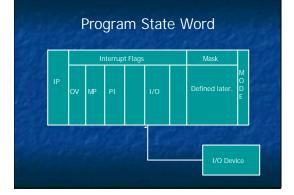

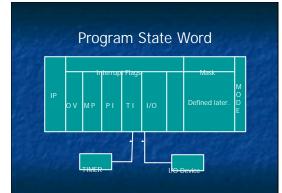

The Program State Word (PSW) is a device that gives us information about the program's current state.

In this register we have the IP, MODE, Interrupt Flags, and Mask (to be defined later).

#### **Privileged Instruction**

What would happen if a user program tried to modify a register that shouldn't be changed, such as the FENCE register?

Clearly we don't want to change the FENCE value, however, the FENCE register is not protect under the memory protection mechanism.

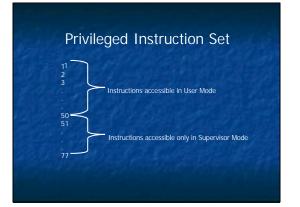

By using the idea of privileged instructions we are able to deno te which instructions are allowed by the user program and which one s are prohibited (system only instructions).

#### **Privileged Instructions**

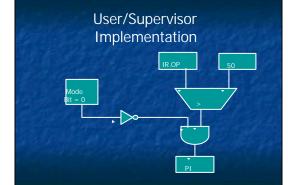

The computer needs a way to distinguish when privileged instructions are allowed and when they aren't.

This can be accomplished by operating in two distinct modes.

User Mode – 0

Supervisor Mode- 1

When in user mode, the program is restricted to limited set of instructions.

When in the CPU is in supervisor mode, all instruction are available.

#### 05 Interrupt Cycle

If OV = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow 1$ If MP = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow 1$ If PI = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow 1$ DECODER  $\leftarrow 00$  (ABEND). (ABEND). (ABEND).

#### Types of Interrupts

Software Interrupts

Traps – Overflow Problem

System Calls – The program tells the O.S. to do something for it.

Hardware (I/O) Interrupt – When the operation assigned to the O.S. is completed, a signal is sent.

External (Timer) - Implemented to protect against an infinite loop.

## 05 Interrupt Cycle

If OV = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow 1$ If MP = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow 1$ If PI = 1 THEN IP ← NEWIP; MODE ← 1 If I/O = 1 THEN OLDIP  $\leftarrow$  IP IP  $\leftarrow$  NEWIP MODE  $\leftarrow$  1

(ABEND). (ABEND). (ABEND).

> (ABEND). (ABEND). (ABEND).

DECODER ← 00

## **Timer Interrupts** A device is needed to prevent a program from "hogging" the CPU.

This is done by setting a timer once a program starts. If the program has not completed by the time the timer gets to zero, the Timer Interrupt (TI) bit is set to 1.

This transfers control to the Interrupt Handler.

## 05 Interrupt Cycle

If OV = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow$  1 If MP = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow$  1 If PI = 1 THEN IP  $\leftarrow$  NEWIP; MODE  $\leftarrow$  1 If I/O = 1 THEN OLDIP ← IP  $IP \leftarrow NEWIP$ MODE ← 1

DECODER ← 00

## SuperVisorCall (SVC)

An SVC is also known as a System Call.

It is a mechanism to request service from the Supervisor or OS.

This mechanism is a type of interrupt, called a *software interrupt* because the program itself relinquishes control to the Supervisor as part of its instructions.